DDR3内存参数

发布时间:2019-09-17 07:48:50编辑:auto阅读(4223)

我们先来看一看技术规格对比表,从表中可以看到DDR3内存相对于DDR2内存,其实只是规格上的提高,并没有真正的全面换代的新架构。

| DDR1 | DDR2 | DDR3 | |

| 电压 VDD/VDDQ | 2.5V/2.5V | 1.8V/1.8V (+/-0.1) | 1.5V/1.5V (+/-0.075) |

| I/O接口 | SSTL_25 | SSTL_18 | SSTL_15 |

| 数据传输率(Mbps) | 200~400 | 400~800 | 800~2000 |

| 容量标准 | 64M~1G | 256M~4G | 512M~8G |

| Memory Latency(ns) | 15~20 | 10~20 | 10~15 |

| CL值 | 1.5/2/2.5/3 | 3/4/5/6 | 5/6/7/8 |

| 预取设计(Bit) | 2 | 4 | 8 |

| 逻辑Bank数量 | 2/4 | 4/8 | 8/16 |

| 突发长度 | 2/4/8 | 4/8 | 8 |

| 封装 | TSOP | FBGA | FBGA |

| 引脚标准 | 184Pin DIMM | 240Pin DIMM | 240Pin DIMM |

1、逻辑Bank数量

DDR2 SDRAM中有4Bank和8Bank的设计,目的就是为了应对未来大容量芯片的需求。而DDR3很可能将从2Gb容量起步,因此起始的逻辑Bank就是8个,另外还为未来的16个逻辑Bank做好了准备。

2、封装(Packages)

DDR3由于新增了一些功能,所以在引脚方面会有所增加,8bit芯片采用78球FBGA封装,16bit芯片采用96球FBGA封装,而DDR2则有60/68/84球FBGA封装三种规格。并且DDR3必须是绿色封装,不能含有任何有害物质。

3、突发长度(BL,Burst Length)

由于DDR3的预取为8bit,所以突发传输周期(BL,Burst Length)也固定为8,而对于DDR2和早期的DDR架构的系统,BL=4也是常用的,DDR3为此增加了一个4-bit Burst Chop(突发突变)模式,即由一个BL=4的读取操作加上一个BL=4的写入操作来合成一个BL=8的数据突发传输,届时可通过A12地址线来控制这一突发模式。而且需要指出的是,任何突发中断操作都将在DDR3内存中予以禁止,且不予支持,取而代之的是更灵活的突发传输控制(如4bit顺序突发)。

4、寻址时序(Timing)

就像DDR2从DDR转变而来后延迟周期数增加一样,DDR3的CL周期也将比DDR2有所提高。DDR2的CL范围一般在2至5之间,而DDR3则在5至11之间,且附加延迟(AL)的设计也有所变化。DDR2时AL的范围是0至4,而DDR3时AL有三种选项,分别是0、CL-1和CL-2。另外,DDR3还新增加了一个时序参数——写入延迟(CWD),这一参数将根据具体的工作频率而定。

DDR3内存优势何在

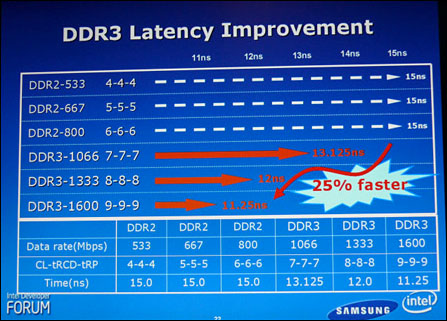

DDR3除了拥有更高的内存带宽外,其实在延迟值方面也是有提升的。不少消费者均被CAS延迟值数值所误导,认为DDR3内存的延迟表现将不及DDR2。但相关专家指出这是完全错误的观念,要计算整个内存模块的延迟值,还需要把内存颗粒的工作频率计算在内。事实上,JEDEC规定DDR2-533的CL 4-4-4、DDR2-667的CL 5-5-5及DDR2-800的CL6-6-6,其内存延迟时间均为15ns。

延迟同样也有提升

CAS Latency(CL)是指内存需要经过多少个周期才能开始读写数据,从前面的DDR/DDR2/DDR3规格表我们可以知道,DDR3的CAS Latency(CL)将在5~8之间,相比现在DDR2的3~6又要高出很多。

目前DDR3-1066、DDR3-1333和DDR3-1600的CL值分别为7-7-7、8-8-8及9-9-9,把内存颗粒工作频率计算在内,其内存模块的延迟值应为13.125ns、12ns及11.25ns,相比DDR2内存模块提升了约25%,因此消费者以CAS数值当成内存模块的延迟值是不正确的。

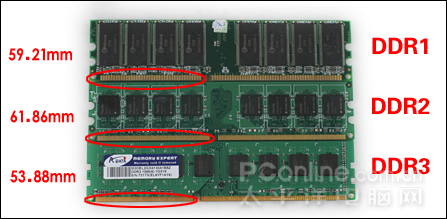

从外观上去看,DDR3内存与我们平时熟悉的DDR2没有太大的改变,如果没有特别留意的话不容易从外观上区分开来。下面我们来看一看DDR3内存与DDR2内存在外观设计上有什么不同之处。

金手指缺口位置

DDR/DDR2/DDR3内存三代同堂

首先是金手指缺口位置作了更改,金手指方面,SDRAM时代是两个缺口位置,升代至DDR时就改成了一们缺口位置,这个缺口位置最大的作用就是避免内存不会插错方向。从上图可以看到,DDR内存金手指离内存端最近的距离为59.21mm,占整个长度约45%左右,到了DDR2时,这个长度改为61.86mm,约占整个长度47%(由于接近50%的比例让不少不太细心的用户容易把内存方向搞错);而DDR3的缺口位置肯定要与DDR和DDR2不同,好在DDR3的缺口位置比例远离50%,53.88mm的距离仅占整个长度约41%,用户可以较明显地区分出内存的方向来。

上一篇: Python资源汇集网站推荐:aweso

下一篇: python中常用的base64 md5

- openvpn linux客户端使用

52679

- H3C基本命令大全

52592

- openvpn windows客户端使用

42730

- H3C IRF原理及 配置

39603

- Python exit()函数

33994

- openvpn mac客户端使用

30958

- python全系列官方中文文档

29753

- python 获取网卡实时流量

24640

- 1.常用turtle功能函数

24482

- python 获取Linux和Windows硬件信息

22863

- LangGraph Studio可视化

210°

- LangSmith开发-应用入门

220°

- LangGraph开发-多轮对话问答机器人

288°

- LangGraph开发-条件分支/循环图实战

273°

- LangGraph开发-生态介绍,入门demo实战

307°

- LangChain-接入12306-HTTP MCP智能体

464°

- LangChain接入自定义爬虫-MCP工具

440°

- LangChain接入Filesystem-MCP工具

456°

- LangChain搭建MCP服务端和客户端流程

528°

- LangGraph与MCP技术概述

450°

- 姓名:Run

- 职业:谜

- 邮箱:383697894@qq.com

- 定位:上海 · 松江